1. Tujuan [Kembali]

Mampu membuat aplikasi carry propagation

Memahami fungsi komponen pada carry propagation

2. Alat dan Bahan [Kembali]

Logicstate

a. Gerbang logika NAND (IC 7010)

Gerbang NAND menghendaki semua inputnya bernilai 0 (terhubung dengan ground) atau salah satunya bernilai 1 agar menghasilkan output yang berharga 1.

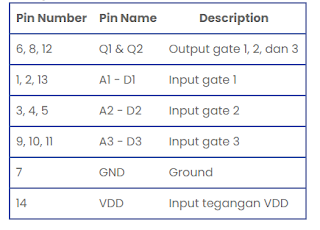

Spesifikasi:

Konfigurasi pin:

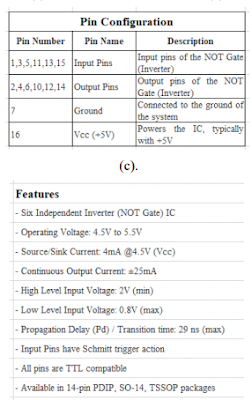

b. Inverter (NOT)

Inverter atau pembalik(NOT) adalah suatu gerbang yang bertujuan untuk menghasilkan logika output kebalikan dari logika input. Adapun simbol dan tabel kebenaran gerbang Inverter seperti berikut:

c. Logic State

Perangkat elektronik yang akan membuat keputusan logis berdasarkan berbagai kombinasi sinyal inputnya. Mungkin memiliki lebih dari satu input tetapi hanya memiliki satu keluaran digital.

d. Logic Probe

Logic Probe berfungsi untuk melihat output.

3. Dasar Teori [Kembali]

a. Gerbang NAND

Gerbang NAND akan menghasilkan keluaran (Output) Logika 0, apabila semua masukan (Input) pada Logika 1 dan apabila ada sebuah masukan (Input) yang bernilai Logika 0, maka akan menghasilkan keluaran (Output) Logika 1.

Transistor Gerbang NAND

Secara sederhana, gerbang logika NAND 2 input dapat dibangun menggunakan RTL Resistor-transistor Switch yang terhubung bersama degan input yang terhubung langsung ke basis transistor, dimana transistor harus dalam keadaan cut-off "MATI" untuk keluaran Q.

Gerbang logika NAND dapat menghasilkan fungsi logis yang diinginkan dengan simbol berupa gerbang AND standar dengan tambahan lingkaran (biasa juga disebut sebagai "Gelembung Inversi" pada bagian output yang mana mewakili gerbang NOT) yang disebut sebagai operasi logika NAND.

Jenis Gerbang Logika NAND:

Gerbang NAND 4 Input:

Berdasarkan gambar diatas ekspresi Boolean untuk gerbang NAND 4 input yaitu : Q = A.B.C.D

b. Inverter(Gerbang NOT)

Gerbang NOT merupakan gerbang di mana keluarannya akan selalu berlawanan dengan masukannya. Bila pada masukan diberikan tegangan ,maka transistor akan jenuh dan keluaran akan bertegangan nol. Sedangkan bila pada masukannya diberi tegangan tertentu, maka transistor akan cut off, sehingga keluaran akan bertegangan tidak nol.

Materi:

Kebanyakan flip-flops memiliki input sinkron dan asinkron.

Input sinkron adalah mereka yang efeknya pada output flip-flop disinkronkan dengan input jam. Input R, S, J, K dan D semuanya adalah input sinkron.

Input asinkron adalah input yang beroperasi secara independen dari input sinkron dan sinyal clock input. Ini sebenarnya menimpa input karena statusnya menimpa status semua input sinkron dan juga input jam. Mereka memaksa output flip-flop untuk pergi ke keadaan yang telah ditentukan terlepas dari status logika dari input sinkron.

Input PRESET dan CLEAR adalah contoh input asinkron. Saat aktif, input PRESET dan CLEAR menempatkan output Q flip-flop masing-masing dalam status '1' dan '0'. Biasanya, ini adalah input LOW yang aktif. Ketika diinginkan agar fungsi flip-flop sesuai dengan status input sinkronisnya, input asinkron disimpan dalam keadaan tidak aktifnya. Selain itu, kedua input asinkron, jika tersedia pada flip-flop tertentu, tidak diaktifkan secara bersamaan.

Alat yang digunakan untuk memasukkan input logika (Boolean 1 dan 2) masukan.

Logicprobe

Alat yang digunakan untuk menganalisa output logika (Boolean 1 dan 2) masukan.

- Bahan

Gerbang XOR

Gerbang XOR ini memerlukan dua input untuk menghasilkan satu output. Jika input berlogika 1 jumlahnya ganjil maka output akan belogika 1. Begitu juga sebaliknya, jika input berlogika 1 jumlahnya genap maka output akan berlogika 0.

Gerbang AND

Gerbang AND ini memerlukan dua atau lebih input untuk menghasilkan satu output. Jika semua atau salah satu inputnya merupakan bilangan biner 0, maka outputnya akan menjadi 0. Sedangkan jika semua input adalah bilangan biner 1, maka outputnya akan menjadi 1.

Gerbang OR

Gerbang ini juga memerlukan dua input untuk menghasilkan satu output. Gerbang OR ini akan menghasilkan output 1 jika semua atau salah satu input merupakan bilangan biner 1. Sedangkan output akan menghasilkan 0 jika semua inputnya adalah bilangan biner 0.

3. Dasar Teori [Kembali]

Carry lookahead adder adalah rangkaian adder yang lebih cepat dalam melakukan penjumlahan biner dengan menggunakan konsep Carry Generate dan Carry Propagate. CLA disebut sebagai penerus ripple carry adder. Sirkuit CLA meminimalkan waktu tunda propagasi melalui implementasi sirkuit kompleks yang terjadi selama penambahan ini dirancang dengan mengubah rangkaian adder pembawa riak (ripple-carry adder) sedemikian rupa sehingga logika carry penambah diubah menjadi logika dua tingkat.

Dalam kasus penjumlah paralel, penambahan biner dari dua angka dimulai ketika semua bit dari augend dan tambahan harus tersedia pada saat yang sama untuk melakukan perhitungan. Dalam rangkaian penambah paralel, keluaran pembawa dari setiap tahap penambah penuh dihubungkan ke masukan pembawa dari tahap orde tinggi berikutnya, oleh karena itu disebut juga sebagai penambah tipe pembawa riak.

Dalam rangkaian penambah seperti itu, tidak mungkin untuk menghasilkan jumlah dan keluaran keluaran dari setiap tahap sampai pengangkutan masukan terjadi. Sehingga akan terjadi tunda waktu yang cukup besar pada proses penambahan , yang dikenal dengan , tunda propagasi carry. Dalam rangkaian kombinasional apa pun, sinyal harus merambat melalui gerbang sebelum jumlah keluaran yang benar tersedia di terminal keluaran.

Pertimbangkan gambar di atas, di mana jumlah S4 dihasilkan oleh penambah penuh yang sesuai segera setelah sinyal input diterapkan padanya. Tetapi input carry C4 tidak tersedia pada nilai kondisi tunak akhirnya sampai carry c3 tersedia pada nilai kondisi tunaknya. Demikian pula C3 tergantung pada C2 dan C2 pada C1. Oleh karena itu, carry harus merambat ke semua tahapan agar output S4 dan carry C5 menyelesaikan nilai kondisi tunak akhirnya.

Waktu propagasi sama dengan delay propagasi dari gerbang tipikal dikalikan dengan jumlah level gerbang di sirkuit. Misalnya, jika setiap tahap penambah penuh memiliki penundaan propagasi 20n detik, maka S4 akan mencapai nilai akhir yang benar setelah 80n (20 × 4) detik. Jika kita memperpanjang jumlah tahapan untuk menambahkan lebih banyak jumlah bit maka situasi ini menjadi jauh lebih buruk.

Jadi kecepatan jumlah bit yang ditambahkan dalam penambah paralel tergantung pada waktu propagasi carry. Namun, sinyal harus disebarkan melalui gerbang pada waktu yang cukup untuk menghasilkan keluaran yang benar atau diinginkan.

Pertimbangkan rangkaian adder penuh yang ditunjukkan di atas dengan tabel kebenaran yang sesuai. Jika kita mendefinisikan dua variabel sebagai carry generate Gi dan carry propagate Pi maka,

Jumlah keluaran dan keluaran carry dapat dinyatakan dalam bentuk carry generate Gi dan carry propagat Pi sebagai

di mana Gi menghasilkan carry ketika kedua Ai dan Bi adalah 1 terlepas dari input carry. Pi dikaitkan dengan propagasi carry dari Ci ke Ci + 1.

Fungsi carry output Boolean dari setiap tahap dalam 4 tahap carry look-ahead adder dapat dinyatakan sebagai:

Dari persamaan Boolean di atas kita dapat mengamati bahwa C4 tidak harus menunggu C3 dan C2 untuk menyebar (propagate) tetapi sebenarnya C4 disebarkan pada saat yang sama dengan C3 dan C2 . Karena ekspresi Boolean untuk setiap keluaran carry adalah jumlah produk sehingga ini dapat diimplementasikan dengan satu tingkat gerbang AND diikuti oleh gerbang OR.

Implementasi tiga fungsi Boolean untuk setiap output carry (C2 , C3 dan C4) untuk generator carry look-ahead carry ditunjukkan pada gambar di bawah.

Analisis Kompleksitas Waktu :

Kita bisa menganggap carry look-ahead adder terdiri dari dua bagian.

Bagian yang menghitung carry untuk setiap bit.

Bagian yang menambahkan bit input dan carry untuk setiap posisi bit.

Keuntungan dan Kerugian dari Carry Look-Ahead Adder :

- Keuntungan

Penundaan propagasi berkurang.

Memberikan logika penambahan tercepat.

- Kekurangan

Sirkuit penambah Carry Look-ahead menjadi rumit karena jumlah variabel meningkat.

Sirkuit ini lebih mahal karena melibatkan lebih banyak perangkat keras.

4. Percobaan [Kembali]

Prosedur Percobaan

1. Buka aplikasi proteus

2. Pilih komponen yang dibutuhkan, pada rangkaian ini dibutukan gerbang XOR, Gerbang AND, dan gerbabng OR.

3. Rangkai setiap komponen menjadi rangkaian yang diinginkan

4. Ubah spesifikasi komponen sesuai kebutuhan

5. Jalankan simulasi rangkaian.

Rangkaian Simulasi

Prinsip Kerja

Rangkaian carry look-ahead adder jika dilihat pada rangkaian tabel kebenaran menggunakan 2 gerbang XOR, 2 gerbang AND, dan 1 gerbang OR. Ada 3 kondisi yang dihasilkan ketika input diatur pada logicstate sedemikian rupa. Jika input A, B, C adalah 0, 0, 0, 0 maka output di Ci+1 adalah 0 maka kondisi ini adalah no carry generate artinya tidak dihasilkan carry. Kemudian untuk kondisi selanjutnya jika input A, B, C adalah 0, 1, 1 maka output di Ci+1 adalah 1 maka kondisi ini adalah no carry propagate artinya tidak ada carry yang disebarkan. Kemudian untuk kondisi selanjutnya jika input A, B, C adalah 1, 1, 0 atau 1, 1, 1 maka output di Ci+1 adalah 1 maka kondisi ini adalah carry generate artinya carry yang dihasilkan.

5. Video [Kembali]

6. Link Download [Kembali]

download video rangkaian

download html

Tidak ada komentar:

Posting Komentar